EE 333 Exam 2 Summer 2002 Name \_\_\_\_\_

Instructions: All problems are worth 8 points except problem 6 which is worth 12 points. This is an open-book, open-notes exam. All work and answers should appear on the exam sheets. You need not show your work but partial credit may be given even if the answer is not right if work is shown that is leading to the correct solution. Unless specifically stated to the contrary, assume all operational amplifiers are ideal and all MOS transistors are from a process with  $u_n C_{OX}=100ua/v^2$ ,  $V_{TN}=-V_{TP}=1V$ ,  $u_p=u_n/3$ ,  $\lambda=0$ ;  $\gamma=0$ ,.

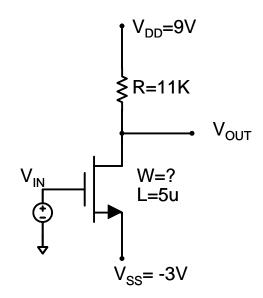

Problem 1 Assume the quiescent output voltage for the following circuit was measured to be -2V. Determine the width of the transistor.

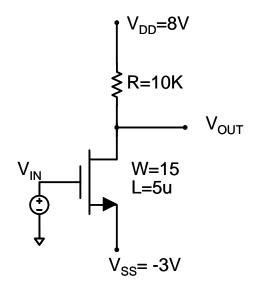

Problem 2 For the amplifier shown, assume that the device dimensions are as indicated.

- a) Determine the steady state output voltage if  $V_{in} = .05sin(500t)$ .

- b) If  $V_{in}=V_m sin(600t)$ , determine the maximum value of  $V_m$  that can be used without causing the MOSFET to leave the saturation region.

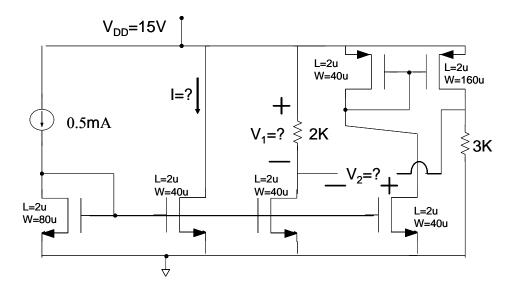

Problem 3 For the circuit shown, determine the variables indicated with a ?.

Problem 4 Assume a 2-port network is characterized by the equations

$$I_1 = 2V_1V_2$$

$$I_2 = 3V_1^2 + 2e^{\frac{V_2}{2}}$$

- Determine a small-signal equivalent circuit at the operating point  $V_{1Q}=3$ , a)  $V_{2Q}$ =1 Determine the quiescent currents  $I_{1Q}$  and  $I_{2Q}$  at the operating point given in a)

- b)

Problem 5 Using the definition for  $t_{HL}$  and  $t_{LH}$  given in class, obtain  $t_{HL}$  and  $t_{LH}$  at the output for the following circuit.

Problem 6 Assume the voltage sources VDD and VGG are such that all 3 transistors are operating in the saturation region. If the capacitor C is very large, determine the small signal voltage gain in terms of the small signal parameters of the transistors.

| _ |    |     |     | _   |

|---|----|-----|-----|-----|

| D | ra | h   | lem | - 7 |

|   |    | ,,, | СШ  |     |

a) Obtain the Boolean expression for the output variable G

b) Using static CMOS, design a circuit at the transistor level that implements the following Boolean function. Assume only the Boolean inputs A,B and C are available. You need not size the devices.